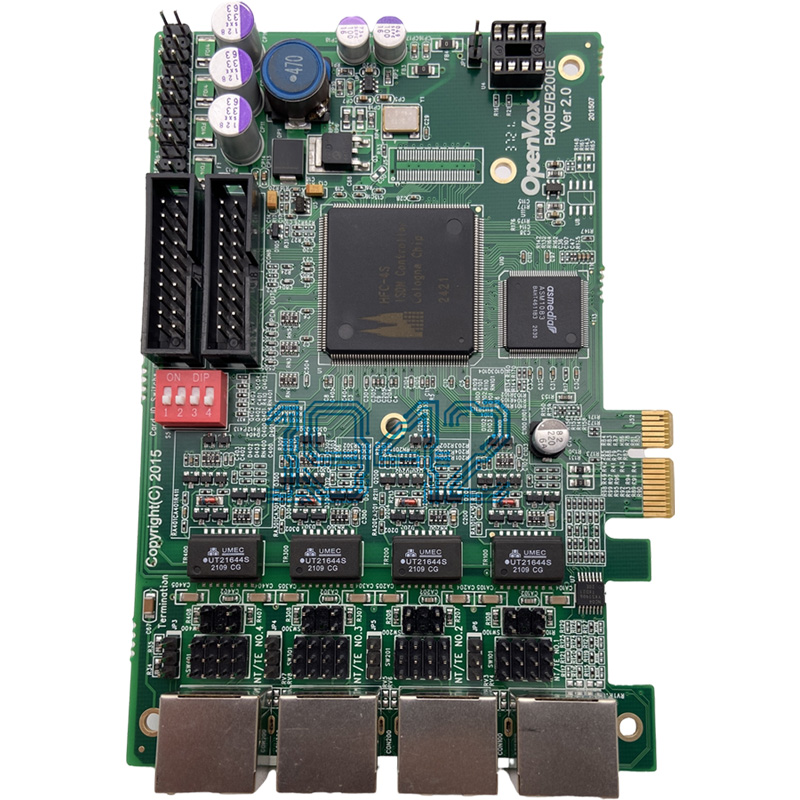

在工業現場復雜電磁環境中,PCBA電路板的信號完整性面臨嚴峻挑戰。高頻噪聲、強電磁干擾(EMI)以及高速信號傳輸需求,對差分線設計提出了更高要求。蛇形差分線作為高速信號傳輸的關鍵結構,其布局合理性直接影響信號抗干擾能力和系統穩定性。本文結合PCBA加工工藝特點,探討如何通過優化設計降低串擾,提升SMT貼片加工后的產品可靠性。

一、蛇形差分線設計核心原則

-

等長與對稱性控制

蛇形差分線的核心目標是保證正負信號路徑長度嚴格一致,以維持差分信號的相位平衡。在PCBA加工中,需通過精密的CAM(計算機輔助制造)軟件對線路進行補償設計,避免因SMT貼片加工誤差導致信號偏移。建議采用45°圓弧彎曲替代直角轉折,減少阻抗突變點。 -

阻抗匹配與線寬優化

差分線阻抗需與驅動端、接收端終端阻抗匹配。在強干擾場景下,可通過適當縮小線寬(如從6mil調整至5mil)并增加銅箔厚度,提升抗干擾能力。同時,需與PCBA加工廠確認疊層設計,確保介質厚度、介電常數等參數滿足阻抗控制要求。

二、抗串擾設計關鍵技術

-

間距與耦合控制

差分對內間距(S)與線寬(W)的比值(S/W)直接影響近端串擾(NEXT)。建議S/W控制在1~2倍之間,避免因間距過小導致耦合過強。對于多組差分線并行布局,需保持組間間距大于3倍線寬,并利用地層隔離減少跨區域串擾。 -

屏蔽與接地策略

在強電磁干擾環境中,可在差分線兩側增加接地通孔陣列(Via Fence),形成法拉第籠效應。通孔間距建議不超過信號波長的1/20,同時確保SMT貼片加工時通孔焊盤無空洞。對于關鍵信號,可采用共面波導結構,通過地平面包裹信號線進一步抑制輻射。 -

蛇形結構參數優化

蛇形線的彎曲半徑(R)需大于3倍線寬,以減少信號反射。相鄰彎曲段間距(P)應大于2R,避免局部耦合。在SMT加工中,需與貼片機工程師確認吸嘴壓力參數,防止薄壁區域因應力變形導致開路。

三、PCBA加工與SMT貼片協同優化

-

層疊設計與殘銅率控制

高速信號層應緊鄰完整地平面,且差分線所在層殘銅率低于40%,以降低介質不均勻性引發的阻抗波動。在SMT貼片加工前,需通過DFM(可制造性設計)檢查確認線路密度,避免因拼板利用率過高導致工藝偏差。 -

焊盤與過孔設計

差分線終端焊盤需采用淚滴狀過渡,減少應力集中。背鉆孔工藝可有效消除過孔殘樁對高頻信號的影響,但需在SMT加工階段控制鉆孔深度公差(±2mil以內),避免損傷內層信號。 -

材料選型與工藝適配

選用低損耗基材(如Megtron 6)可降低介質損耗,但需注意其Tg值(玻璃化轉變溫度)需與SMT貼片加工的回流焊溫度匹配。對于超細間距設計(如0.3mm pitch BGA),需采用激光鉆孔+電鍍填孔工藝,確保信號完整性。

四、測試與驗證

完成PCBA加工后,需通過時域反射計(TDR)測試差分線阻抗,并利用眼圖分析儀評估信號質量。在強電磁干擾環境下,可增加近場探頭掃描,定位輻射熱點并優化屏蔽措施。

結語

在工業4.0背景下,PCBA設計需兼顧高速信號傳輸與抗干擾能力。通過蛇形差分線的精細化設計、SMT貼片加工的工藝控制以及多層級屏蔽措施,可顯著提升系統在強電磁干擾環境下的可靠性。未來隨著5G、AIoT等技術的普及,差分線設計將進一步向高頻、高密度方向發展,這對PCBA加工的精度與工藝協同提出了更高要求。

因設備、物料、生產工藝等不同因素,內容僅供參考。了解更多smt貼片加工知識,歡迎訪問深圳PCBA加工廠-1943科技。

2024-04-26

2024-04-26